# Photonic-Electronic Integrated Circuits for High-Performance Computing and AI Accelerators

Shupeng Ning , Hanqing Zhu, Chenghao Feng, Member, IEEE, Jiaqi Gu, Member, IEEE, Zhixing Jiang, Zhoufeng Ying, Jason Midkiff, Sourabh Jain, May H. Hlaing, David Z. Pan, Fellow, IEEE, and Ray T. Chen, Fellow, IEEE

(Invited Paper)

Abstract—In recent decades, the demand for computational power has surged, particularly with the rapid expansion of artificial intelligence (AI). As we navigate the post-Moore's law era, the limitations of traditional electrical digital computing, including process bottlenecks and power consumption issues, are propelling the search for alternative computing paradigms. Among various emerging technologies, integrated photonics stands out as a promising solution for next-generation high-performance computing, thanks to the inherent advantages of light, such as low latency, high bandwidth, and unique multiplexing techniques. Furthermore, the progress in photonic integrated circuits (PICs), which are equipped with abundant photoelectronic components, positions photonic-electronic integrated circuits as a viable solution for highperformance computing and hardware AI accelerators. In this review, we survey recent advancements in both PIC-based digital and analog computing for AI, exploring the principal benefits and obstacles of implementation. Additionally, we propose a comprehensive analysis of photonic AI from the perspectives of hardware implementation, accelerator architecture, and software-hardware co-design. In the end, acknowledging the existing challenges, we underscore potential strategies for overcoming these issues and offer insights into the future drivers for optical computing.

Index Terms—AI accelerator, optical computing, optical neural network, photonic integrated circuit, silicon photonics.

#### I. INTRODUCTION

A S THE semiconductor industry advances to process nodes below 3 nanometers, it increasingly encounters inherent physical limitations of both devices and materials [1], [2]. A

Manuscript received 15 March 2024; revised 21 June 2024; accepted 10 July 2024. Date of publication 15 July 2024; date of current version 16 November 2024. This work was supported by AFOSR under Grant FA9550-23-1-0452 and Grant FA9550-17-1-0071. (Shupeng Ning and Hanqing Zhu are co-first authors.) (Corresponding author: Ray T. Chen.)

Shupeng Ning, Hanqing Zhu, Chenghao Feng, Zhixing Jiang, Zhoufeng Ying, Jason Midkiff, Sourabh Jain, May H. Hlaing, David Z. Pan, and Ray T. Chen are with the Department of Electrical and Computer Engineering, The University of Texas at Austin, Austin, TX 78712 USA (e-mail: chenrt@austin.utexas.edu).

Jiaqi Gu is with the Department of Electrical and Computer Engineering, The University of Texas at Austin, Austin, TX 78712 USA, and also with the School of Electrical, Computer and Energy Engineering, Arizona State University, Tempe, AZ 85281 USA.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JLT.2024.3427716.

Digital Object Identifier 10.1109/JLT.2024.3427716

primary concern is the surge in power consumption as clock frequencies reach gigahertz levels, leading to overwhelming heat generation [2], [3]. Furthermore, at these diminutive scales, quantum uncertainties begin to dominate electron behavior, resulting in increased transistor errors and reduced reliability. Additionally, AI has made remarkable strides in recent years, exerting a growing influence on various aspects of our lives, such as image recognition [4], [5], [6], [7], natural language processing [8], [9], autonomous driving [10], and medical diagnosis [11], [12], which have further increased societal demand for computational power. One notable example is the emergence of large language models (LLMs) such as GPT (Generative Pre-trained Transformer). These models exhibit human-level intelligence and have revolutionized a wide range of applications, from sophisticated chatbots to advanced text analysis tools. However, the advancements of deep neural networks (DNNs) are driven by rapidly increasing model sizes and data volumes, which necessitate significantly expanding computational demands. For instance, the GPT-3 model developed by OpenAI, which contains around 175 billion parameters, requires 14.8 days for training using a cluster of around 10,000 NVIDIA V100 GPUs, with an estimated energy consumption of 1287 MWh [13], [14], [15]. Hence, in the post-Moore's Law era, traditional electronic computing architectures, designed to execute sequential, digital programs, are inadequate to meet the surging demand for high-performance computing and AI tasks. There is a pressing need to develop processing units capable of performing high-speed, energy-efficient computing. In response, both industry and academia are actively exploring alternative avenues from novel materials [16], [17], architectures [4], [18], to the investigation of new computational paradigms.

Among the emerging technologies, integrated photonics is a promising candidate for next-generation computation that can overcome the bottlenecks of their electrical counterparts. First, the speed of optical signals travel within optical waveguides surpasses that of electron-based transit through transistors with multiple fanouts by 1-2 orders of magnitude [19]. The delay and loss in waveguides are primarily determined by the optical path length. Additionally, a series of high-speed and energy-efficient

0733-8724 © 2024 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

(operating on the order of sub-picojoule per bit) devices for optical computing have been developed [20], [21], [22]. Notably, the power consumption of transistor-based electrical circuits exhibits a cubic relationship with the clock frequency f [23], whereas photonics-electronic platforms scale only linearly with f [24], effectively relaxing the frequency constraints associated with the power wall issue. Furthermore, as bosons, photons do not conform to the Pauli exclusion principle, allowing for the utilization of unique multiplexing techniques such as wavelength division multiplexing (WDM), which further increases the overall bandwidth. Moreover, compared to another photonic computing scheme in the form of free-space diffraction [25], [26], integrated photonics offers superior compactness for higher-level integration. The advancement of silicon photonics has enabled the implementation of optical computing on low-cost PICs with high integration density, leveraging CMOS-compatible silicon manufacturing techniques. As an increasing number of foundries develop their validated process design kits (PDKs), the integrated photonics industry is progressively moving towards standardization similar to that of the fabless semiconductor industry [27]. This trend not only improves accessibility for designers and users but also offers more reliable performance.

Integrated photonics has emerged as a promising platform for AI accelerators, benefiting from its inherent attributes of high parallelism, low latency, and low power consumption. In the last decade, a diverse range of PIC-based optical neural networks (ONNs) that implement multilayer perceptrons (MLPs) [28], convolutional neural networks (CNNs) [26], [29], [30], spiking neural networks (SNNs) [31], [32], etc., have been reported, demonstrating remarkable performance on machine learning tasks. The fundamental operations of neural networks, involving data transfers and tensor operations, are achieved through the combination of passive optical devices and high-performance active photonic-electronic components [33], [34]. Specifically, optical signals can be modulated by electrical signals and "multiplied" in accordance with the transmission function of the PIC. The hybrid photonic-electronic platform combines the adaptability of electronic control with the high-speed capabilities of optical computing. Recently, cutting-edge optical processing units have been reported with a matrix processing speed of 3.8 trillion operations per second (TOPS) via time-wavelength multiplexing [30], while other works demonstrated ultra-low power consumption on the order of sub-femtojoules per bit [22].

While integrated photonics offers new opportunities, existing photonic-electronic computing systems still encounter several practical challenges, such as:

- The typical micron-scale dimensions of optical elements in PICs are significantly larger than the transistors in cuttingedge VLSI technologies. Besides, a range of practical issues, such as footprint, control complexity, and accumulated loss, etc., limit the functionality and scalability of PICs for advanced computing applications.

- The widespread reliance on electrical components for electro-optical (E-O) modulation, parameter updates, data transfer, and analog-to-digital/digital-to-analog (A/D, D/A) conversion in photonic-electronic platforms leads to considerable energy consumption.

The inherent challenges in PICs, such as training algorithms, on-chip implementation of nonlinearity for ONNs and system robustness against noise and crosstalk, require careful consideration in both hardware design and software coordination.

This review focuses on recent progress in photonic-electronic integrated circuits for computing. Spanning from digital computing to analog AI accelerators, this paper is structured as follows. Section II begins with an overview of the fundamental blocks in PIC-based digital computing, followed by a survey of recent highlights ranging from the implementation of logic gates to fully functional photonic processing units. Section III focuses on the implementation of ONNs, covering aspects of photonic tensor cores, nonlinearity, and hardware-aware training strategies. Beyond a review from the device and circuit level, Sections IV and V provide a comprehensive analysis of recent photonic AI efforts from the perspectives of accelerator architectures and software-hardware co-design, respectively. The review culminates with Section VI, which offers an outlook on PIC-based optical computing and provides a summarizing conclusion

## II. SURVEY OF OPTICAL DIGITAL COMPUTING WITH PICS

PICs are comprised of a range of optical components, both passive and active, featuring various hardware implementations and circuit topologies to fulfill distinct functionalities. This section will focus on E-O digital logic, and provides a concise overview of recent progress in PIC-based digital computing, while highlighting these implementation techniques and associated challenges.

## A. Optical Logic Gates

In the digital domain, both input and output are binary, and the resolution is defined by the number of bits and remains unaffected by the circuit size. A range of building blocks for optical digital computing on integrated photonic platforms, such as optical switches [35], modulators [22], [36], interconnects and photodetectors [37], [38], [39], [40], have been experimentally demonstrated. Basic logic operations (NOT, AND, OR, XOR, etc.), which are fundamental elements of digital systems, have been implemented by diverse PICs. Among these, electro-optic logic, also known as optical-directed logic, has been widely investigated by many research groups as well as foundries. As shown in Fig. 1(a), all E-O devices in the functional block, such as Mach-Zehnder Interferometers (MZIs), microring resonators (MRRs), microdisks, etc., are simultaneously configured by electrical signals. When light traverses the block, optical signals are modulated to execute logic operations in accordance with the PIC design and then propagated downstream or detected by monitors to read out the results. An important feature of the E-O digital logic is that each device is controlled by independent electrical input simultaneously and that signals are transmitted via light without the limitation of RC time constant and delay accumulations inherent in electrical systems. In other words, E-O logic merges the convenience and flexibility of electrical control with the high-speed capabilities of optical

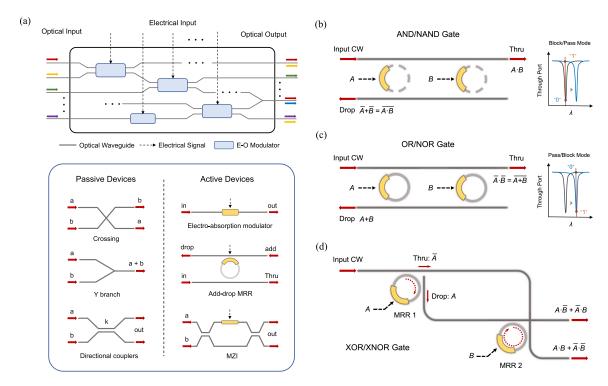

Fig. 1. Implementations of electro-optic logic gates. (a) Schematic diagram of E-O logic composed of passive and active optical components. During each clock cycle, electrical inputs are used to configure the logic circuit, while light carries out logic operations based on the transmission characteristic of the logic block. (b)–(d) Schematic of MRR-based AND/NAND, OR/NOR, and XOR/XNOR gates, as proposed in Ref [41], [42]. In the diagram, the dotted line and the solid line represent MRRs functioning in the "block/pass" and "pass/block" modes, respectively. These configurations correspond to the outputs of "0" and "1" at the through port, given a logic "0" as the electrical input.

computing. Fig. 1(b)-(c) show examples of E-O logic gates using two cascaded MRRs to perform 2-input AND/NAND and OR/NOR operations [41]. The proposed optical logic gate leverages the transmission characteristic of add-drop MRRs, which work as optical switches to implement logic operations and generate complementary outputs at the through and drop ports. Additionally, by configuring the resonant states of MRRs with "0" operands via selecting continuous wave (CW) inputs at either on-resonance or off-resonance wavelengths, a single photonic circuit can execute a variety of logic functions. With consistent logic but varying PIC topologies, XOR and XNOR gates featuring a crossbar structure also have been demonstrated [42] (Fig. 1(d)). Operating with similar mechanisms, MZI-based optical gates have also been extensively developed [43], [44].

In addition to E-O modulation, all-optical logic gate devices have also attracted attention. These devices have been experimentally demonstrated using various structures and phenomena, including photonic crystals [45], [46], surface plasmon polaritons (SPPs) [47], nanowire networks [48], and slot waveguides [49], [50]. A comprehensive classification, explanation of mechanisms, and comparative analysis of all-optical logic gates has been detailed in the prior review [51], [52], [53]. Compared to E-O logic, all-optical logic offers the potential for higher operation speed and bandwidth without extra energy consumption associated with O-E-O conversion. However, the implementation of all-optical logic confronts several practical challenges. Firstly, the complexity and requirements of design

and fabrication (e.g., the transmission characteristic of photonic crystal is highly sensitive to its lattice constant) lead to inherent instability and a low contrast ratio between logical states [50]. Secondly, while all-optical gates can be more energy-efficient in signal processing, they often require higher optical signal power (mW-level) to compensate for higher losses or to induce the necessary nonlinear effects for switching. Furthermore, the limited functionality and scalability of all-optical logic, coupled with its higher cost, restrict its widespread application compared to E-O logic.

In recent years, integrated photonics have expanded beyond traditional classical optics, emerging as a compelling platform for quantum information science. Quantum logic gates based on the aforementioned active/passive devices have been widely reported [54], [55], [56]. Quantum PICs offer several significant advantages over bulk optics in the realm of quantum computing. First, PICs enable precise control of phase, polarization, and spatial mode with higher stability, which are essential for manipulating quantum states. Second, silicon exhibits a high thirdorder nonlinear coefficient  $\chi^{(3)}$ , facilitates the effective implementation of on-chip single/entangled photon sources through optical processes such as four-wave mixing (FWM) [57]. Third, PICs can integrate the fundamental building blocks of quantum computing-such as photon source, modulators, and singlephoton detectors, etc., -in monolithic, hybrid, or heterogeneous configurations [58]. This integration yields scalable, robust, and reconfigurable circuits capable of handling complex quantum computing tasks [57], [59], [60].

# B. Combinational Logic and Reconfigurable PICs

In digital circuits, the output of a combinational logic unit is determined solely by the current input combination, without dependence on previous states. Similarly, the implementation of optical combinational logic could begin with extracting the logical expression from its truth table, followed by designing the corresponding PIC based on the simplified expression. The implementation can rely on assembling fundamental logic gates or leveraging the unique characteristics of optical components or multiplexing techniques for fewer devices and compact layouts. Employing these strategies, diverse optical combinational logic units, including but not limited to adders [61], comparators [62], encoders [63], [64] and decoders [65], have been reported.

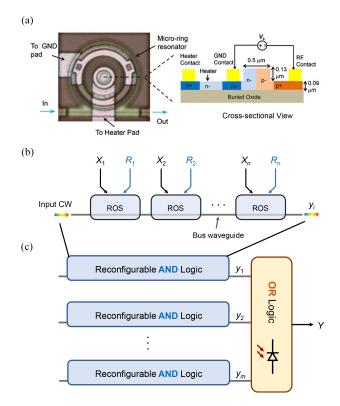

The aforementioned optical logic gates and units, tailored for specific tasks, are constrained by a fixed or limited logic representation. The inherent limitation not only complicates the development process but also increases the cost. To address this challenge, reconfigurable PICs offer a promising solution by programming the operational states of optical switches within a pre-designed framework using additional signals. The input operands and the reconfiguration signal can be independently managed by two separate control units within the modulator, such as the dual arms of MZIs. Generally, reconfiguration signals do not require high-speed modulation to the same extent as the input signals used as logic operands. Qiu et al. proposed a reconfigurable logic unit based on MRRs embedded with two modulation mechanisms [66]. As is shown in Fig. 2(a), the logic operand is modulated at high speeds via the *p-i-n* junction operating in the carrier injection mode, while the resonant state of MRR can be reconfigured using the microheater. Additionally, multi-operand modulators and non-volatile devices are also promising candidates for reconfigurable PICs [67], [68], [69].

An arbitrary combinational logic expression Y with n inputs  $X_1, X_2, \ldots, X_n$  can be represented as a sum of products derived from these inputs, which can be expressed as:

$$Y = y_1 + y_2 + \ldots + y_m$$

, where  $y_i = \prod_{k=1}^n X_k$  or  $\overline{X_k}$  (1)

In this expression,  $\overline{X_k}$  denotes the complement logic of input  $X_k$ . Using reconfigurable optical switches, the architecture illustrated in Fig. 2(b)-(c) theoretically can implement arbitrary logic functions conforming to the expression format presented in (1). The product term  $y_i$ , i.e., the logic AND operation, can be implemented by n serially connected reconfigurable optical switches along single bus waveguides. This block yields logic "1" output only when all switches are in the "pass" state. Reconfiguration signals  $R_i$  are used to determine whether the corresponding operand contributes complement logic to  $y_i$ . In contrast to electrical digital computing, the OR operation for optical signals can be directly implemented using a combiner and detected by a photodetector. It is important to recognize that when product terms are represented by the same wavelength, the amalgamation may result in logical errors due to coherent interference. This issue can be avoided either by using distinct wavelengths for each branch [66], or equipping each branch with photodetectors individually [70]. Besides, given that photodetectors operate as

Fig. 2. Reconfigurable PICs for arbitrary combinational logic. (a) Optical micrograph and cross-sectional diagram of a reconfigurable MRR featuring two modulation mechanisms. The p-i-n junction is applied by RF signal for input encoding, while the microheater is connected to the low-speed DC signal for resonance mode reconfiguration [66]. (b) and (c) Schematic of a PIC architecture that enables the implementation of arbitrary combinational logic expressions based on reconfigurable optical switchs (ROSs).

current sources, a straightforward parallel configuration could achieve electrical OR logic without introducing additional delays. While this strategy offers a general solution for optical combinational logic, the limited scalability restricts its practical applicability in scenarios involving numerous operands. For an n-operands system, the complexity of this processing unit escalates as  $O(n \cdot 2^n)$ , indicating an exponential increase in the requisite number of switches with n. Furthermore, issues related to power consumption and accumulated losses also need to be considered. The dynamic power of the system  $P_{\rm dynamic}$  can be expressed as:

$$P_{\rm dynamic} = \frac{1}{4}\alpha C V^2 f \tag{2}$$

where,  $\alpha$  is the activity factor and C is the total capacitance of the E-O modulators, which increases proportionally with the number of modulators. It is important to note that while (2) has a similar expression to that used for CMOS transistors, the supply voltage V does not necessarily scale with f. Therefore, to reduce  $P_{\rm dynamic}$ , two straightforward strategies can be considered: 1) Decrease the number of modulators, for example, by employing multi-operand logic gates to squeeze logic functions into fewer devices [68]; 2) Utilize devices with low capacitance, such as microdisks with capacitance in 10's fF [24]. Additionally, when present, thermal tuning typically dominates the power consumption for modulation. This portion of power consumption can be

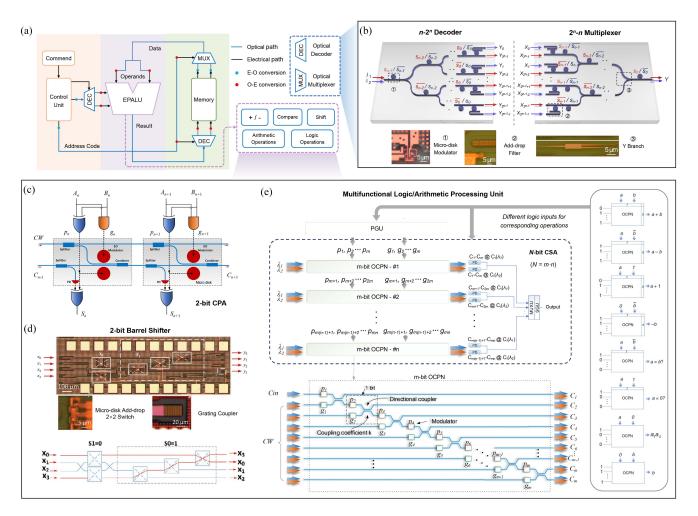

Fig. 3. EPALU architecture for high-performance digital computing. (a) Schematic of electronic–photonic microprocessor with its building blocks and data path. (b) Schematic of an n- $2^n$  E-O decoder and  $2^n$ -n O-E multiplexer [79], where  $s_i$  refers to the electrical input signal. (c) Schematic of a 2-bit CPA using E-O logic [61]. (d) Layout of a 2-bit barrel shifter using microdisk add-drop switch array, and the optical datapath with S = '01' [77]. (e) The architecture of the WDM-based N-bit multifunctional processing unit consists of a (p, g) generation unit (PGU), n sets of m-bit optical carry propagation networks (OCPNs), and an array of photodetectors (PDs) along with a network of electronic multiplexer units (MUXU) and an electronic sum generation unit (SGU) [24]. With different input combinations, EPALU can perform various logic/arithmetic functions (right).

reduced or even eliminated through device-level optimization, such as post-fabrication trimming [71], or using energy-efficient tuning mechanisms (discussed in Section III-A). The total power consumption also includes the laser and detection parts, as well as the potential static power consumption. The laser power is primarily determined by the losses, typically at the mW level with dB/cm-level loss, which also correlates with the PIC scale.

In the realm of electrical digital design, electronic design automation (EDA) tools assist designers by automatically generating and optimizing circuits from logic expressions, as well as auto-placing and routing in physical design. With the advancement of PIC-based computing, logic synthesis methods specified for PIC design have been proposed, enabling large-scale design automation and optimization of compact PICs for digital computing [72], [73], [74].

# C. Toward a Fully-Functional EPALU

Besides the aforementioned advantages of optical logic units, unique multiplexing techniques play a pivotal role in further improving computing capacity and performance. An example is the WDM-based electronics-photonic arithmetic logic unit (EPALU) (Fig. 3(a)) [24]. The arithmetic logic unit (ALU), which performs arithmetic and bitwise operations, is an essential component of modern computing systems. Within ALUs, the full adder plays a critical role, with its logic being expressed as follows:

$$C_n = p_n \cdot C_{n-1} + g_n , \quad S_n = C_{n-1} \oplus p_n$$

$$g_n = A_n \cdot B_n , \quad p_n = A_n \oplus B_n$$

(3)

where A, B, and C represent the two operands and carry, respectively; p and g denote propagation and generation, and the subscripts indicate the specific bits. Based on these expressions, the scalable electro-optic carry propagation adder (CPA) has been developed [61], with the schematic shown in Fig. 3(c). For a N-bit CPA, the carry output from one stage is the carry input to the next stage, thus the final result cannot be calculated until the carry has rippled through all stages. As an optimized architecture, the carry select adder (CSA) splits N-bit operands into

n m-bit CPA  $(N = m \times n)$ . It speeds up addition by computing two possible outcomes for each m-bit CPA simultaneouslyassuming carry-in values of "0" and "1"-and then selects the correct result based on the actual carry-in using multiplexers (MUXs) [75]. As a trade-off, CSAs require two sets of circuits with different carry inputs. However, in the optical domain, this can be efficiently implemented with a single optical path in the PIC, where different carry signals are encoded into two distinct wavelengths using WDM (Fig. 3(e)). Beyond arithmetic addition, Ying et al. developed that the multifunctional architecture could perform addition, subtraction, comparison, and bitwise operations operating at 20 GB/s with various input combinations [24]. Based on time-space multiplexing, Zhang et al. demonstrated a photonic-electronic digital multiplier capable of processing up to  $32 \times 4$ -bit binary inputs at 25 Mbit/s [76]. Additionally, the E-O shifter within the EPALU architecture has also been experimentally demonstrated (Fig. 3(d)) [77].

From the perspective of computer architecture, the ALU operates under the directives issued by electronic control units, with its inputs being fetched from memory. Upon completing a designated operation, the ALU's output is then stored back in memory to be accessed for subsequent computations (Fig. 3(a)). Although optical computing has significantly reduced the latency of arithmetic operations, data access and E-O/O-E conversions can create major bandwidth bottlenecks and serve as a significant source of energy consumption in the computing system. Therefore, the exploration of high-speed interconnects between different modules within an electronic-photonic microprocessor is important as well [78], [79]. In [79], a decoder and multiplexer designed for the EPALU architecture have been demonstrated, achieving data transportation and processing at a speed of 20 Gb/s (Fig. 3(b)). Another potential approach to reduce the time and energy costs of E-O/O-E conversion is through the implementation of various forms of optical memory, as discussed in [80], [81].

# III. PIC-BASED ANALOG COMPUTING FOR AI: FUNDAMENTALS AND IMPLEMENTATION

Undoubtedly, modern AI, functioning on digital computing systems, has achieved significant progress in diverse fields and has even exceeded human performance in specific tasks. With the advancements in integrated photonics, the PIC platform emerges as a compelling candidate for AI accelerators. Leveraging the optical logic gates and computing units detailed in Section II, some studies have illustrated the capability of PICs to perform tensor operations, including accumulation, dot products, and matrix-vector multiplications (MVMs), for diverse machine learning applications within the digital domain [82], [83], [84]. These studies have highlighted the inherent advantages of optical computing in terms of latency, speed, and power efficiency. However, the digital representation can encounter challenges stemming from hardware complexity overhead and speed reduction caused by the sampling and digitization into binary streams processed by logic units. These challenges are especially significant in the context of high-throughput or high-precision tensor operations for various machine-learning tasks.

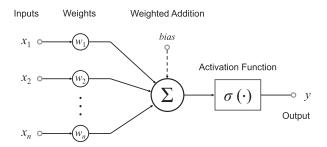

Fig. 4. Schematic of an artificial neuron with simple synaptic model.

On the other hand, the human brain, operating as an analog signal "processor", is estimated to perform at a rate of  $10^{18}$ multiply-accumulate (MAC)/s with a power consumption estimated at just  $\sim$ 10–20 W [85], [86], demonstrating remarkable efficiency compared to the substantial energy requirements of cutting-edge AI. This efficiency can potentially be attributed to the parallel processing capability and reduced precision requirements inherent in analog computing. While the mechanisms of brain function remain incompletely understood, there is growing interest in incorporating analog computing into machine learning. Before discussing the details of implementing optical analog computing for AI, it is helpful to provide a concise overview of artificial neural networks (ANNs) and the neuron model. The schematic of an artificial neuron with a basic synaptic model is illustrated in Fig. 4, where x, y, and w represent the inputs from the pre-synaptic neuron, post-synaptic output, and weights of the connection, respectively. The activation functions  $\sigma(\cdot)$ , such as sigmoid, ReLU, and the leaky integrate-and-fire (LIF) function for SNNs, introduce nonlinearity into the model along with various engineering considerations [87], [88].

# A. Programmable Modulation for Optical Analog Computing

In analog AI accelerators, both inputs  $\mathbf{x}$  and weights  $\mathbf{w}$  could correspond to a higher resolution, in contrast to the binary values in digital computing circuits. The hardware implementation of the above process using PICs requires the reconfigurable programming of network parameters, which relies on the modulation of optical components. While the weights in a trained model may remain fixed during the inference process, it is still necessary to calibrate the network through modulation due to the fabrication variations of PICs. A number of modulation mechanisms have been developed, among which tuning the effective refractive index  $n_{\rm eff}$  of waveguides is a widely adopted approach in ONNs.

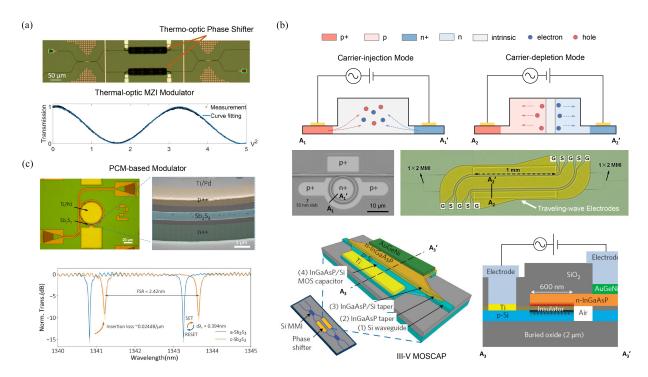

1) Thermal Tuning Mechanism: Based on thermo-optic effects, the transmission characteristics of devices can be modulated by changing the  $n_{\rm eff}$  of waveguide through integrated filament microheaters. The heat generated by the ohmic microheater is proportional to the square of the bias voltage. Fig. 5(a) shows the schematic and transmission curve of a thermo-optic MZI fabricated by Advanced Micro Foundry [89]. Thermal tuning demonstrates the adaptability to various devices and substrate materials, with minimal constraints imposed by the fabrication process. Furthermore, compared with other mechanisms (especially for silicon), it can induce large changes in  $n_{\rm eff}$  within a

Fig. 5. Modulation techniques of photonic-electronic devices on PICs. (a) Optical micrograph and the normalized transmission curve of a thermo-optic MZI. Each arm of the MZI incorporates a microheater as a phase shifter [89]. While both arms can be used to modulate the output signal, typically, one is used to set the modulator output at the quadrature point for a high extinction ratio in monotonic modulation. (b) Schematics and micrographs of free-carrier effect-based modulators working in carrier-injection mode [110], carrier-depletion mode [95], and by the MOSCAP-driven tuning mechanism [98]. (c) Top, optical micrograph of an MRR modulator loaded with  $10 \mu m \log 20$ -nm-thick  $Sb_2S_3$  and doped silicon PIN heater. Bottom, normalized transmission spectra of MRR when switching between two phases of  $Sb_2S_3$  [109].

small footprint. However, thermo-optic devices encounter difficulties in achieving high-speed modulation, currently limited to a few hundred KHz [90], although sufficient for inference tasks with static weights. Additionally, thermal tuning is a volatile configuration process, requiring continuous external biasing and power supply (typically ~mW level) to hold its functionality. Another issue arises from thermal crosstalk when heat dispersion cannot be adequately contained without physical constraints, such as trenches, which need appropriate consideration in both schematic and layout design.

2) Field-Effect Tuning Mechanism: Except for the thermooptic effect, the  $n_{\rm eff}$  can also be tuned by electric fields. In silicon photonics, a straightforward approach involves doping the silicon waveguide and applying an external electric field to manipulate the carrier concentration and tune  $n_{\rm eff}$ . A variety of modulators operating in carrier-injection (forwardbias p-i-n), carrier-depletion (reverse-bias p-n junction), and carrier-accumulation (metal-oxide-semiconductor capacitor, MOSCAP) mode have been widely demonstrated (Fig. 5(b)) [91], [92], [93], [94], [95], [96]. These CMOS-compatible mechanisms allow gigahertz-level tuning speeds, making them suitable for high-speed encoding in ONNs. Particularly, in depletion mode, the bandwidth is determined by the majority carriers' dynamics, which are not limited by the slower processes of carrier generation and recombination [94]. Moreover, while the depletion-mode modulator remains a volatile device, it exhibits low static power consumption attributed to the reverse-biased junction. Compared to thermo-optic devices, the free-carrier effect-based modulators typically require longer modulation

lengths and larger footprints, primarily due to their lower tunning efficiencies (as evaluated by voltage-length product  $V_\pi L$ ) or the necessity for traveling-wave electrodes for high-speed modulation. Expanding beyond the conventional silicon platform, an alternative approach is the utilization of materials with significant electro-optic effects—such as the free-carrier plasma dispersions, the Pockels effect, the Kerr effect, and the Quantum Confined Stark Effect (QCSE)—for the core or cladding of waveguides. The modulation efficiency of these devices is intrinsically linked to the material properties. Prominent examples include III–V semiconductors [96], [97], [98], lithium niobate [99], and some polymers [100], [101]. A comprehensive discussion of all these mechanisms exceeds the scope of this review. Interested readers are referred to relevant reviews and reports for further information [102], [103], [104].

Most modulators discussed above have nonlinear transmission curves, primarily due to the E-O modulation mechanisms involved. Although the Pockels effect provides a linear change in  $\Delta n$  in response to electric field intensity, the inherent transfer function of the modulator itself can still exhibit a nonlinearity (such as the sinusoidal response of MZI). To reduce undesired nonlinearity in computing architectures, several solutions have been proposed: 1) Introduce a nonlinear mapping during D/A conversion, although this may necessitate additional data processing; 2) Utilize the nearly linear segment of the transmission curve, at the tradeoff of a reduced modulation dynamic range; 3) Design PICs that compensate for nonlinearity by novel devices or modulation mechanisms [100], [105], [106], [107], [108]. Additionally, the impact of nonlinearity on system noise also needs

| Mechanism         | $V_{\pi}L$ (V·cm)     | IL (dB)  | $f_{ m 3dB}$                 | Data Rate | Energy Efficiency                   | Active Length        | Modulator | Ref   |

|-------------------|-----------------------|----------|------------------------------|-----------|-------------------------------------|----------------------|-----------|-------|

| Thermo-optics     | ~0.023                | <1       | ∼4 KHz                       | _         | ~1.36 mW*                           | ~170 µm              | MZM       | [89]  |

| Carrier Injection | 0.036                 | 12       | 16 GHz                       | 10 Gb/s   | 51 mW* / 5 pJ/bit                   | $200~\mu\mathrm{m}$  | MZM       | [92]  |

| Carrier Depletion | 1.62-2.05             | 3.9      | 30 GHz                       | 44 Gb/s   | 2.84 pJ/bit                         | $1000~\mu\mathrm{m}$ | MZM       | [95]  |

| Si-MOSCAP         | $\sim 0.8$            | 9        | 50 GHz                       | >100 Gb/s | _                                   | $R = 15 \mu m$       | MRR       | [96]  |

| III-V-MOSCAP      | 0.09                  | 1        | 2.2 GHz                      | 32 Gb/s   | _                                   | $250~\mu\mathrm{m}$  | MZM       | [98]  |

| Graphene-MOSCAP   | 0.28                  | $\sim 7$ | 5 GHz                        | 10 Gb/s   | 1 pJ/bit                            | $300~\mu\mathrm{m}$  | MZM       | [111] |

| PCM               | $L_\pi$ =30.7 $\mu$ m | <1       | $\sim \! 10 \; \mathrm{KHz}$ | _         | 11.6 mJ for SET<br>197 nJ for RESET | $R = 30 \mu m$       | MZM/MRR   | [109] |

TABLE I SUMMARY OF MODULATION TECHNIQUES WITH SILICON WAVEGUIDE

consideration. Within modulators exhibiting strong nonlinearity and steep slopes, such as high-Q MRRs, slight noise or offsets in the drive signal can potentially result in significant deviations.

3) Non-Volatile Modulation: Each aforementioned mechanism is a volatile process and requires continuous power supply even for infrequent or static programming tasks. Non-volatile phase change materials (PCMs) offer a unique opportunity to avoid these scenarios. PCMs have two switchable phases, i.e. amorphous and crystalline states, with drastically different  $n_{\rm eff}$ , and can achieve reversible phase transitions within various temperature ranges. For the PIC platform, heating can be achieved by an integrated pulse microheater or alternatively, through light signals themselves, enabling 'all-optical' modulation. Chen et al. developed several non-volatile silicon photonics modulators with Sb<sub>2</sub>S<sub>3</sub> PCM cladding and experimentally demonstrated 5-bit multilevel programming with a high cyclability >1600 switching events (Fig. 5(c)) [109]. Besides, all-optical SNNs using chalcogenide PCM GeSbTe (GST) also have been reported [32], and more details will be discussed in Section. III-C2. A brief summary of modulation techniques with Si waveguide is shown in Table I.

## B. Implementations of Photonic Tensor Cores

As illustrated in Fig. 4, the interconnections in ANNs can be conceptualized as weights akin to synaptic coupling coefficients in biological systems. This analogy extends to representing these connections through tensor operations, thereby abstracting the complex interactions in a computationally manageable form. Building upon the aforementioned modulation mechanisms, various active devices and encoding mechanisms have been utilized effectively in photonic neurons. This section categorizes ONNs from multiple perspectives, which aims to provide a comprehensive analysis and comparison of the implementations of photonic tensor cores (PTCs) from diverse optical components to the architectural design.

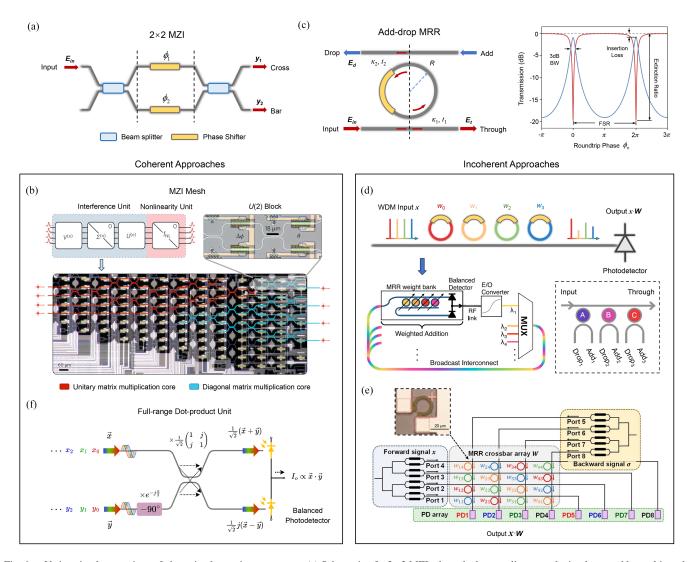

1) Coherent vs Incoherent ONN: From the viewpoint of signal properties, ONNs can be classified into coherent and incoherent systems. Within coherent ONNs, both weights and inputs can be encoded in the complex plane, allowing multiplication through lossless interference. For instance, a pair of beam splitters and phase shifters in the form of MZIs are widely adopted for conducting linear operations in coherent ONNs due

to the programmable amplitude and phase response [112]. The schematic of a  $2\times 2$  MZI is shown in Fig. 6(a). Assuming that each beam splitter is an ideal 50:50 directional coupler (i.e., with a coupling coefficient  $\kappa=1/\sqrt{2}$ ), the transition matrix of the MZI can be represented as:

$$T_{\text{MZI}} = \frac{1}{\sqrt{2}} \begin{bmatrix} 1 & j \\ j & 1 \end{bmatrix} \cdot \begin{bmatrix} e^{-j\phi_1} & 0 \\ 0 & e^{-j\phi_2} \end{bmatrix} \cdot \frac{1}{\sqrt{2}} \begin{bmatrix} 1 & j \\ j & 1 \end{bmatrix}$$

(4)

Here,  $\phi_1$  and  $\phi_2$  represent the phase changes as signals traverse two arms. In some cases,  $\phi_1$  and  $\phi_2$  are denoted as  $\Delta \phi = \phi_1 - \phi_2$  and 0, respectively, given that the response is predominantly governed by the phase difference between its two arms. If only one input port receives a signal  $E_{\rm in}$ , the field and power intensities at the output port can be expressed as follows:

$$y_1 = -j \cdot \exp\left[-j\left(\phi_2 + \frac{\Delta\phi}{2}\right)\right] \cdot \sin\left(\frac{\Delta\phi}{2}\right) \cdot E_{\text{in}};$$

$$y_2 = j \cdot \exp\left[-j\left(\phi_2 + \frac{\Delta\phi}{2}\right)\right] \cdot \cos\left(\frac{\Delta\phi}{2}\right) \cdot E_{\text{in}}$$

(5)

$$|y_{1,2}|^2 = |E_{\rm in}|^2 \cdot \frac{1 \mp \cos \Delta \phi}{2}$$

(6)

This implies that the phase and amplitude of output can be modulated by varying  $\Delta\phi$  from 0 to  $\pi$ . The smooth transmission curve, stemming from the cosine term, enables high-resolution analog computing and enhances noise resistance. In a notable case, the two arms are encoded by opposite phase shifts, represented as  $\phi \pm \Delta\phi/2$  for  $\phi_1$  and  $\phi_2$ , respectively. When incorporated into (4), the Mach-Zehnder modulator (MZM) working in "push-pull" mode allows for the independent modulation of field intensity while maintaining a constant phase.

An MZI cascaded with a phase shifter can implement a  $2\times2$  unitary transformation:

$$U(2) = \overbrace{\left[ \begin{array}{cc} e^{-j\theta} & 0 \\ 0 & 1 \end{array} \right]}^{\text{Phase Shifter}} \cdot \overbrace{\frac{1}{2} \left[ \begin{array}{cc} e^{-j\Delta\phi} - 1 & j(e^{-j\Delta\phi} + 1) \\ j(e^{-j\Delta\phi} + 1) & -(e^{-j\Delta\phi} - 1) \end{array} \right]}^{\text{MZI}}$$

$$= \frac{1}{2} \begin{bmatrix} e^{-j\theta} (e^{-j\Delta\phi} - 1) & je^{-j\theta} (e^{-j\Delta\phi} + 1) \\ j(e^{-j\Delta\phi} + 1) & -(e^{-j\Delta\phi} - 1) \end{bmatrix}$$

(7)

<sup>\*</sup> Static power consumption

$<sup>\</sup>sim$  Measured from figures or calculated based on other parameters in the articles

<sup>-</sup> Not mentioned or unavailable in the article

Fig. 6. Various implementations of photonic-electronic tensor cores. (a) Schematic of a  $2\times2$  MZI where the beam splitters can be implemented by multi-mode interferometer (MMIs) or directional couplers. An alternative configuration of MZI features a single input and output, with the splitter designed as a Y branch. (b) An MZI-based coherent photonics tensor core for ONNs [28]. The weight matrix can be represented by SVD in the form  $U\Sigma V^{\dagger}$ . Due to chip size and complexity considerations, this work only implements U and  $\Sigma$  on a single pass through the circuit. (c) Schematic and power spectral responses of an add-drop MRR with power coupling coefficients  $\kappa_1^2 = \kappa_2^2 = 0.2$  (assuming the coupling junctions are lossless, i.e.,  $\kappa^2 + t^2 = 1$ ) and 5% round-trip power loss. (d) The weight bank architecture utilizes MRRs as tunable filters for parallel modulation of WDM signals [122]. The series-connected MRRs share a single bus waveguide as a through port, while the other waveguide can be shared or independent, enabling the selective addition or removal of wavelengths. (e) Schematic of  $4\times4$  MRR crossbar array demonstrated in Ref [123]. Input signals are first modulated via MZMs, and then distributed and weighted through the crossbar array, followed by a photodetector array that sums the weighted WDM elements. (f) The Schematic of an optical tensor core supports dynamic full-range general matrix multiplication based on WDM and coherent interference [126].

Unitary matrices of rank N can be decomposed into sets of U(2) blocks, which can be implemented using cascaded  $2\times 2$  MZIs to form a mesh structure. Despite the unitary nature of the transition matrix in an MZI-mesh, an arbitrary weight matrix for an ONN can be implemented by singular vector decomposition (SVD). The SVD approach was thoroughly discussed by Miller et al. in 2003 and first experimentally implemented in ONNs by Shen et al. as shown in Fig. 6(b) [28], [113]. Specifically, an arbitrary real-valued matrix M can be decomposed into the form  $U\Sigma V^{\dagger}$ , where  $\Sigma$  is a diagonal matrix and the remaining two are unitary matrices, which can be implemented with a set of tunable attenuators and an MZI mesh, respectively.

Another characteristic of the devices based on phase modulation is their broad spectral bandwidth. During the modulation process, the phase change  $\psi$  can be expressed as follows:

$$\psi = \frac{2\pi L_{\rm PS} \Delta n_{\rm eff}}{\lambda} \tag{8}$$

where  $\lambda$  and  $L_{PS}$  represent operating wavelength and effective modulation length. Within the C-band and O-band commonly used in silicon photonics, the transmission characteristic demonstrates a low sensitivity to  $\lambda$  over a range of several tens of nanometers. Particularly for thermo-optic devices, the thermal

modulation coefficient  $dn_{eff}/dT$  shows a slight increase corresponding to the increase in wavelength, which compensates for the decrease in wave number  $2\pi/\lambda$  [114]. Therefore, an MZM followed by a phase shifter can achieve parallel modulation of multiple signals with different wavelengths based on WDM. However, it should be noted that waveguides induce different phase changes at various  $\lambda$ , which must be considered when using WDM in coherent ONNs.

Thanks to the phase encoding mechanism, coherent ONNs can perform multiplication with full-range input operands. Besides the SVD approach, a more intuitive example is that the sign and absolute value of the scalar can be encoded by the phase shifter and MZM separately. Following this methodology, [115] presents a photonic neuron architecture enabling full-range dot product operations. However, this architecture also faces limitations in terms of complexity and scalability. Specifically, implementing SVD required a matrix pre-processing step for phase mapping, which consumes extra time and power. In addition, the number of MZIs escalates quadratically with matrix size, leading to scalability issues due to the larger footprint and accumulated losses. Moreover, the phase control of the coherence network presents a challenge as well. Within the MZI mesh, each U(2) operation demands a minimum of two active phase modulators. Without a reference signal, phase calibration becomes more complex than amplitude calibration (which can be straightforwardly measured using photodetectors), especially considering the fabrication deviation across individual devices and waveguides. However, some studies demonstrate the feasibility of addressing the phase calibration issue through on-chip training [116], [117].

Incoherent PICs offer an alternative approach to execute tensor operations. In the absence of coherence requirements, an incoherent ONN enables broader flexibility in employing multiplexing techniques. Because of its wavelength-dependent transmission characteristics, MRRs are widely employed for encoding weights and inputs in WDM-based incoherent ONNs. From the perspective of physical design, the small footprint of MRR (achieving a radius <10  $\mu$ m) affords a compact layout and an enhanced scalability. As shown in Fig. 6(c), the add-drop MRR is a four-port optical device that consists of a microring evanescently coupled to two bus waveguides. The transfer characteristics at the through port and drop port can be expressed as (9) and (10).

$$T_t = \left| \frac{E_t}{E_{in}} \right|^2 = \frac{t_1^2 + t_2^2 \alpha_{rt}^2 - 2t_1 t_2 \alpha_{rt} \cos \phi_{rt}}{1 + t_1^2 t_2^2 \alpha_{rt}^2 - 2t_1 t_2 \alpha_{rt} \cos \phi_{rt}} \tag{9}$$

$$T_d = \left| \frac{E_d}{E_{in}} \right|^2 = \frac{\kappa_1^2 \kappa_2^2 \alpha_{rt}}{1 + t_1^2 t_2^2 \alpha_{rt}^2 - 2t_1 t_2 \alpha_{rt} \cos \phi_{rt}}$$

(10)

Here,  $\kappa$  and t represent the field coupling factor and transmission factor, respectively.  $\alpha_{rt} = exp(-\alpha \cdot 2\pi R)$  and  $\phi_{rt} = \beta \cdot 2\pi R$  are the round-trip field attenuation factor and phase, with  $\alpha$  and  $\beta$  being the real and imaginary parts of the complex transmission coefficients [118]. The resonance condition is  $\phi_{rt} = 2m\pi$ , i.e.,  $\lambda_{\rm res} = 2\pi n_{\rm eff} R/m$ , where m is a positive integer. A potential issue in achieving full-range modulation (i.e., from 0 to 1) arises, as it can only be attained with symmetric, lossless coupling

$(\alpha_{rt}=1,\ t_1=t_2)$ , which is unrealistic for real devices. An all-pass MRR can be regarded as a special case of an add-drop MRR, distinguished by the absence of a drop bus waveguide with  $t_2=1$  and  $\kappa_2=0$  for (9). While the phase at the through/drop port can also be derived from (9) and (10), the phase response and tuning range are highly sensitive to coupling conditions and round-trip loss. Hence, MRRs are primarily employed for amplitude modulation in incoherent systems. Another challenge comes from the experimental perspective: MRRs, particularly those with high quality factors, are sensitive to environmental factors such as temperature variations and vibrations. For a more in-depth theoretical analysis of MRRs, readers may refer to relevant literature and books [118], [119].

In tensor operations, MRRs can be modulated by tuning coupling coefficients or the round-trip phase [120]. Unlike MZIs, MRRs demonstrate significant wavelength selectivity. An MRR with a moderate quality factor can achieve a resonance peak with a 3 dB bandwidth of a few hundred picometers. The narrow bandwidth makes MRRs particularly effective as tunable filters in WDM-based PICs, where they are often arranged in series for the selective modulation of signals with different wavelengths. This application is exemplified by the concept of "weight banks" proposed by Tait et al. [121], [122], as shown in Fig. 6(d). In this architecture, photodetectors can spontaneously perform the sum of operands encoded on different wavelengths. Another incoherent architecture is the crossbar array, which implements MVMs using its programmable transfer matrix in the form of a tunable switch array [123], [124], [125]. Ohno, et al. demonstrated a 4×4 add-drop MRR crossbar array for MVMs (Fig. 6(e)) [123]. Specifically, each wavelength coming from the row bus waveguide can be weighted and subsequently directed into a specific column by the MRR array. The weighted elements can be collected and aggregated by a photodetector at the end of the column, thus carrying out MVM.

A notable constraint of incoherent ONNs is the challenge of directly implementing negative operands due to the amplitude modulation mechanism. An intuitive solution is dividing the matrix into positive and negative parts, subsequently mapping into the network up to 4 times to execute  $(X_+ - X_-)(Y_+ - Y_-)$ , and thereafter deducting the outcomes within the electrical domain. Alternatively, the positive and negative components can be processed simultaneously through two identical incoherent hardware networks. Both strategies, however, necessitate either extended processing time or increased hardware resources. Another strategy leverages the complementary output from the through and drop ports of the add-drop, enabling the full-range output as demonstrated in the work of Tait et al. [121], [122]. For the last two approaches, the post-processing subtraction can be physically implemented using balanced photodetectors, as illustrated in Fig 6(d).

2) Static and Dynamic Weight Encoding: The abovementioned architectures topically map one operand of MVMs (typically a weight matrix W) onto hardware, executing multiplication through the transmission matrix of the PIC. Therefore, the operational speed of an ONN is, in theory, only determined by the modulation rate of input signals x. However, practical implementations face several limitations. Primarily, deploying MVMs with large dimensions is challenging due to the cost, complexity, loss, and other scalability issues of PICs. While multiplexing techniques can enhance the parallelism of ONNs, time-domain hardware reuse is necessary to fulfill the computational requirements of complex machine learning tasks. This indicates that the "weight-static" architecture constitutes a bottleneck for large networks because of the huge gap between ultra-fast optical computing and slow mapping/reprogramming. To fully unleash the potential of optical analog computing, the critical role of dynamic encoding for specific tasks should be recognized. For dynamically-operated ONNs, two essential requirements must be satisfied. First, the parameters in the network need to be high-speed reprogrammable for efficient hardware reuse. This requires that the modulators operate at gigahertzlevel rates, as exemplified by those based on field-effect tuning mechanisms. Secondly, dynamic operation mandates that parameter mapping and output reading be conducted "directly" without additional signal preprocessing or data correction. For instance, to map a 12×12 matrix to an MZI-mesh framework requires  $\sim 1.5$  ms to perform SVD and phase decomposition on a CPU [126], which precludes dynamic operation due to the delay.

The importance of dynamic encoding is further highlighted by its compatibility with *Transformer* [9]. Transformer and the unique attention mechanisms have attracted significant research interest in recent years due to their exceptional performance in natural language processing (NLP), machine vision (MV), and large-scale language models (LLM). Unlike weight-static architectures, Transformer employs the multi-head self-attention (MHA) mechanism within its encoder and decoder blocks, necessitating matrix multiplication involving two dynamic, fullrange operands. Zhu et al. presented a dynamically-operated PTC for the first photonic Transformer accelerator, leveraging coherent light interference and WDM [126]. As shown in Fig. 6(f), the elements within the input vectors x and y are encoded at distinct wavelengths, and then add a  $-90^{\circ}$  phase shift to one vector. Through a directional coupler, two orthogonal signals can be recombined into the form  $(x \pm y)$ , facilitating the computation of the dot product via a balanced photodetector.

3) Hardware-Efficient PTCs: For the aforementioned structures, the total number of optical components required to implement an  $m \times n$  general matrix is similar, e.g.,  $m(m-1)/2 + n(n-1)/2 + \max(m,n)$  MZIs for an SVD-based MZI mesh, and  $m \times n$  MRRs in microring-based ONNs. In addition to the high hardware costs and inherent control complexities, the required electrical components make up a large proportion of energy consumption, particularly for high-speed and high-resolution modulation. To address these challenges, researchers are exploring strategies to enhance hardware efficiency across multiple levels—from the device to the architecture—to improve the scalability of ONNs.

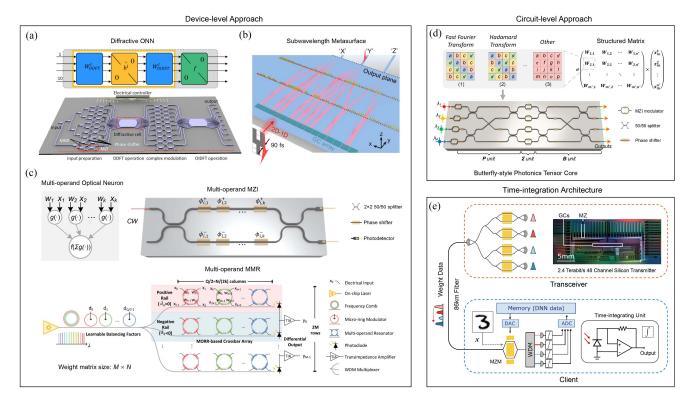

Firstly, optical devices or structures featuring compact topology have been proposed to reduce PIC footprint and improve hardware efficiency. Zhu et al. developed an ONN architecture consisting of two diffractive cells and MZIs exhibiting linear scaling in relation to input dimensions [127], as shown in Fig. 7(a). The star-shaped diffractive cell shows the capability of

performing on-chip parallel Fourier transform and convolution operations. In a similar vein, an ONN leveraging the combination of WDM and MMIs has been developed and demonstrates an accuracy of 92.17% on the MNIST dataset. Beyond waveguide-based PIC, Wang et al. proposed a metasurface-based processing unit that provides ultra-high throughput for MVM [128] (Fig. 7(b)). Within the subwavelength structure, each pair of slots acts as a weight element and connects to the following layers via in-plane diffraction and interference. For a specific neural network, the width and length of the slot need to be designed to map the corresponding weights.

The passive ONNs not only yield smaller footprints and enhanced hardware efficiency but also lower power consumption. However, a significant challenge associated with the passive task-specific PTCs is their fixed configuration, which can lead to degraded effectiveness when applied to varying tasks. To address this challenge, active multi-operand devices present another opportunity to break the fundamental limitation to achieve high-density tensor operation by squeezing MAC operation into a single device. Specifically, the execution of the length-k dot product between input vector  $\boldsymbol{x}_{\text{in}}$  and weight vector  $\boldsymbol{w}$  by k-operand devices can be represented as follows:

$$x_{\text{out}} = f(\boldsymbol{w} \cdot \boldsymbol{x}_{\text{in}}) = f\left(\sum_{i=1}^{k} g(w_i, x_i)\right)$$

(11)

where the function  $f(\cdot)$  represents the E-O transmission function, while g(w, x) is related to the encoding mechanism. Here, w can be encoded using programmable resistances (such as memristors or PCMs), tunable amplifiers/attenuators, or the effective modulation length in cases, while  $x_{

m in}$  can be encoded by electrical signals. The type of multi-operand devices can either be the modulators mentioned above or based on other passive optical components such as MMI [129]. Feng et al. first demonstrated this method experimentally on a 4-operand MZI, achieving a measured accuracy of 85.9% in SVHN recognition tasks with 4-bit control precision (Fig. 7(c)). Gu et al. proposed a compact ONN architecture based on multi-operand MRRs (MOMRR) [130]. The MOMRR-based ONN supports weight encoding through two sets of rails, with full-range results carried out by balanced photodetectors [131]. Additionally, the architecture can be combined with the structured pruning strategy to further improve network scalability. Theoretically, multi-operand optical synapses could execute vector operations with nearly the same footprint as the single-operand counterparts. However, the intrinsic nonlinearity and possible crosstalk among operands could present challenges for training and calibration.

Beyond improvements at the device level, another promising approach enhances hardware efficiency at the circuit level by software-hardware co-design approaches. Subspace neural networks, for instance, sacrifice a portion of matrix representability in exchange for fewer parameters instead of implementing universal linear operations or general matrix multiplication (GEMM). The effectiveness of this strategy can extend to ONNs by trading the universality of weight representation for higher hardware efficiency. An example is the butterfly-style PTC [89] (Fig. 7(d)). By parameter pruning, this architecture

Fig. 7. Implementation of hardware-efficient PTCs. (a) and (b) Schematics of space-efficient ONNs using compact diffractive cell [127] and metasurface structure [128], respectively. O(I)DFT: Optical (inverse) discrete Fourier transform (c) Diagram of a multi-operand optical neuron, along with schematics of multi-operand MZI [130] and multi-operand MRR [131]. (d) The general architecture of the subspace ONNs (top), and schematic of  $4\times4$  butterfly-style tensor core (bottom) [89]. Here, B and P are both unitary matrices and  $\Sigma$  is a diagonal matrix. Here, B and P represent butterfly-style transform unit and projection unit, respectively (e) Architecture diagram of a delocalized time-integration optical computing system consists of smart transceivers as cloud infrastructure and the edge client devices [132]. The parameters of the neural network model are encoded using WDM on the cloud side and transmitted to client nodes via a long-haul optical fiber. The MVMs are carried out in time-integrating of photocurrent generated by the photodetector in the client device.

could be implemented using significantly fewer MZIs with a scale factor of  $O(n\log_2^n)$  rather than the  $O(n^2)$  required by an MZI mesh for GEMM. This study experimentally showcases a measured accuracy of over 94% on the MNIST hand-written digits classification task, with up to  $7\times$  fewer active optical components, a  $3.3\times$  smaller footprint, and a  $5.5\times$  lower latency compared to conventional MZI mesh. A similar strategy, utilizing an MRR-based crossbar array to implement block-circulant matrices, has been demonstrated in Ref [125]. For subspace networks, the trade-off between hardware efficiency and matrix representability is an important consideration, and more details will be discussed in Section V-A.

Beyond the one-shot broadcast architecture, an alternative method leverages time-domain integration with fewer optical components to perform MACs [132], [133]. Following this approach, Sludds et al. developed a delocalized optical computing system that showcases edge computing capabilities over a span of 86 kilometers [132]. As shown in Fig. 7(e), the modulated WDM signals are separated by a passive demultiplexer and then fed to a set of time-integrating receivers. On the client side, only one MZM, ADC, and DAC are used, which allows an ultra-low power assumption of femtojoules per MAC operation. The photocurrent I(t) generated by the photodetector produces a voltage across the integrating capacitor C by accumulating charge, thereby achieving the summation operation, which can

be expressed as (12).

$$V_{\text{out}} = \int \frac{I(t)}{C} dt \propto \sum w_i x_i$$

(12)

This strategy sacrifices the speed benefit of optical computing to achieve a smaller chip footprint and reduced hardware complexity, which enables the use of milliwatt-class edge devices.

# C. Implementations of Nonlinearities

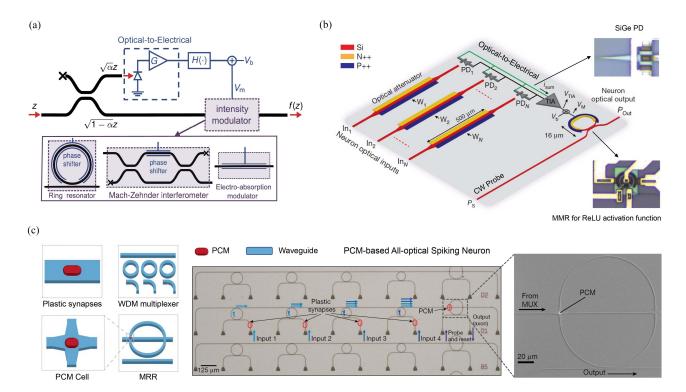

Activation functions introduce the necessary nonlinearity into the network. For PIC-based photonic neurons, the implementations of nonlinearities fall into two major categories: the optical-electrical-optical (O-E-O) and the all-optical approach.

1) O-E-O Nonlinearities: The activation function within O-E-O neurons can be realized most directly by routing the weighted sum through A/D conversion into digital processing units, such as CPUs, GPUs, or FPGAs. This process performs nonlinear operations digitally, and then converts the digital output back into analog signals that are subsequently fed into photonic neurons. The primary advantage of this approach is its extensive transfer ability of existing ANN architectures to the PIC platform, which also facilitates the implementation of arbitrary activation functions. However, the compulsory A/D and D/A conversion, along with digital processing, impose latency

Fig. 8. On-chip implementations of programmable nonlinear activation functions. (a) and (b) Schematics of O-E-O nonlinear units for realization of reconfigurable activation functions [136], [137], [138]. (c) A PCM-based all-optical spiking neuron [32]. The input spikes are weighted via PCM cells, and the PCM cell on the MRR could switch the resonate condition when the accumulated power of the postsynaptic spikes exceeds a predefined threshold, thereby controlling the generation of output spikes.

and power consumption, thereby undermining the efficiency advantage inherent in ONNs. As mentioned in Section II, the performance and speed of an optical computing system are constrained by its weakest link, which in this case is the E-O interface and the digital processing. Alternatively, nonlinearities can also occur in the analog domain by leveraging the inherent nonlinear responses of specific electronic components or analog circuits [134], [135].

Beyond implementing nonlinearity purely in the electronic domain, nonlinearity can also be introduced within the E-O/O-E conversion processes, such as the nonlinear transmission properties of E-O modulators during encoding. For instance, the nonlinear part of the cosine term in the MZM transfer function exhibits similarities to the sigmoid function. This methodology has been validated on the last two layers of an ONN for the MNIST classification task in [115], and a similar approach involving the built-in nonlinearity of MRRs has been proposed by Gu, et al. [131]. The main advantage of introducing nonlinearity in encoding is it does not need extra O-E conversions. However, since the nonlinearity is entirely contingent on the transmission characteristics of E-O modulators, this dependency may pose challenges during the training process. Inappropriate activation functions, particularly in deep networks, can result in gradient vanishing or explosion and low training efficiency. To achieve reconfigurable activation functions, Williamson et al. introduced a nonlinear unit that converts a small portion of the optical output into an electrical signal to modulate the original optical signal (Fig. 8(a)) [136], [137]. This setup offers two approaches for the electrical part. The first approach converts the tapped signal into an electrical signal directly, allowing for moderate adjustments in nonlinearity through varying electrical biases. The second strategy utilizes reconfigurable lookup tables controlled by a microcontroller, which enables the generation of arbitrary nonlinearities and aligns more closely with an all-electrical approach. Likewise, MRRs can be employed to realize this methodology. In [138] and [139], activation functions are implemented by modulating a CW probe with the output from photodetectors (Fig. 8(b)). While this architecture avoids the loss accumulation issue, it requires an additional laser source as the probe. In addition to introducing nonlinearity from E-O modulation, O-E conversion processes, exemplified by the response of photodetectors, can also serve as the source of nonlinearity [140]. Nevertheless, these approaches are also constrained by limited reconfigurability.

2) All-Optical Nonlinearities: Without electrical components, all-optical approaches implement activation functions via the nonlinear response of materials or devices to optical signals. Several ONNs have been demonstrated using semiconductor optical amplifiers (SOAs) [141], saturable absorbers [142], [143], and techniques exhibiting excitable behavior [144]. All-optical nonlinearities can also be achieved by PCMs, such as the all-optical neuron developed by Feldmann et al. [32]. In this work, the PCM, functioning as a waveguide cladding, is used to modulate the pre-synaptic input and govern the resonance state of MRR, thereby controlling the generation of output spikes (Fig. 8(c)). Beyond the issues of activation function applicability

Fig. 9. Optical neural network training methods. (a) Offline training on a digital platform, such as a GPU, mimics the behavior of analog hardware by building a physical model of PICs. (b) Physical neural network training, which utilizes PICs for forward pass and incorporates a differentiable digital model for backpropagation. (c) *In-situ* optical neural network training is performed entirely on photonic hardware.

previously discussed, the implementation of all-optical neurons faces several other challenges. Firstly, even though extra electrical devices are not required, the substantial power required to excite nonlinearities does not offer any power consumption advantages compared to the O-E-O approaches. Additionally, the fabrication and integration of optical components for all-optical nonlinearity, such as PCM, excitable lasers, and optical amplifiers, pose challenges as well. Lastly, since both the control signal and post-synaptic output are optical signals, a potential issue exists in distinguishing the response from the control signals or bias.

## D. Optical Neural Network Training

As an analog computing platform, PICs for AI applications are inherently susceptible to various non-ideal conditions, such as environmental changes, process variation, and limited control precision. These factors can decrease inference accuracy and potentially degrade the signal-to-noise ratio (SNR) of computations. To mitigate the decrease in accuracy, it is crucial to train ONNs with careful consideration of non-idealities that may occur during inference, making it a "circuit-aware" approach will enhance its noise resilience. The current ONN training can be classified into two categories: hardware-aware *ex-situ* training, which involves training with the help of digital computers, and on-chip *in-situ* training.

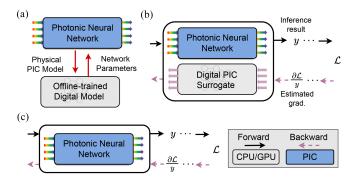

1) Hardware-Aware Ex-Situ Training: Hardware-aware exsitu training offloads the training process to digital computers

and utilizes various hardware-aware training techniques to capture PIC behavior as precisely as possible during training. One

commonly used technique is noise-aware training [145], [146],

as shown in Fig. 9(a). This approach involves modeling the

behavior of PICs while considering various non-ideal effects.

Subsequently, the PIC model is injected into the training to

reduce the gap between training and real inference. Gaussian

noise is commonly used to model various noise sources in

photonic systems. For instance, shot noise and thermal noise

are modeled using a Gaussian distribution by measuring onchip photonic multiplication results and fitting their distribution [132]. In addition to injecting non-idealities into the

training, some work explicitly models the transfer matrix of photonic neurons and embeds them in the forward computation pass during training [130], [131]. This injection is crucial because it introduces a unique nonlinearity term that ONNs need to be aware of in order to accurately capture the behavior of photonic neurons. Moreover, in [126], the noisy transfer matrix is derived and explicitly injected in the training under some noise assumptions. However, this approach encounters two main challenges. Firstly, accurately representing all on-chip non-idealities poses a significant difficulty, and environmental fluctuations can further affect inference accuracy. Second, the computational overhead required to model the physical system accurately can be exceedingly high or even prohibitive, making the training very slow and costly.

Aware of these challenges, some works advocate for training optical neural networks directly with non-ideal physical responses, called physical network training, as shown in Fig. 9(b). The forward pass is executed on PICs and the loss signal  $\mathcal{L}$  is obtained by comparing the physical and intended outputs. However, a challenge arises during the backward pass due to the undifferentiable nature of the physical response. To address this challenge, the idea of adopting a differentiable PIC surrogate model in digital domain has been proposed [89], [147], [148]. With the differentiable model, the gradient of the loss can be propagated back with respect to the controllable parameters. This strategy obviates the need for tedious modeling and analysis of on-chip noise sources, incorporating the noisy behavior of photonic chips naturally during training.

2) In-Situ Training: In-situ training aims to perform training directly on-chip, enabling the inherent consideration of all kinds of on-chip non-idealities, as shown in Fig. 9(c). This approach can potentially boost accuracy to the greatest extent by directly incorporating the real-world behavior of photonic hardware into the training process.

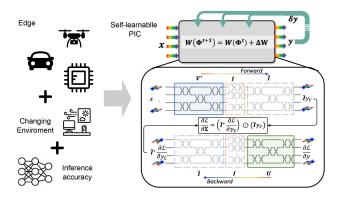

Although *in-situ* training is *straightforward* and *ideal*, it is challenging to implement directly on the optical computing platform. Considering an optical neural network layer l, optical components execute the linear projection  $W^l(\Phi^l)$  complemented by a digital or analog nonlinear transformation  $f^l$ . With the input  $\mathbf{x}^l$ , the forward manner can be defined as,

$$\mathbf{y}^{l} = W^{l}(\mathbf{\Phi}^{l})\mathbf{x}^{l}$$

$$\mathbf{x}^{l+1} = f^{l}(\mathbf{y}^{l}). \tag{13}$$

Here,  $\Phi^l$  represents the device configurations, which are the device control variables. For the backward pass, assuming we can access the gradient of loss over  $\mathbf{x}^{l+1}$ ,  $\partial \mathcal{L}/\partial \mathbf{x}^{l+1}$ , we need to obtain the gradient over input  $\mathbf{x}^l$  and device configurations  $\Phi^l$ . The first step is to obtain the gradient over  $\mathbf{y}^l$ , which could be prohibitive if the activation function is undifferentiable without analytical formulations, especially for customized analog activations. After determining the gradient  $\partial \mathcal{L}/\partial \mathbf{y}^l$ , the gradients over inputs and device configurations are defined as  $W^l(\Phi^l)^T \frac{\partial \mathcal{L}}{\partial \mathbf{y}^l}$  and  $\frac{\partial \mathcal{L}}{\partial \mathbf{y}^l} \mathbf{x}^T \frac{\partial \mathbf{W}^l(\Phi^l)}{\Phi^l}$ . The challenges of obtaining the above two items stem from several aspects. First, it requires bidirectional input support to access the transpose of  $W^l(\Phi^l)$ . Second, one

Fig. 10. In-situ backpropagation concept of adjoint-variable method [151]. The forward, backward, and sum steps of their backpropagation concept are shown to derive the gradient with respect to phase parameters  $\theta$ .

may argue that another optical processor can be used to implement matrix multiplication in the backward pass, thereby avoiding the need for bidirectional support. However, noise and precision limitations cause the gradient computation to deviate from the desired matrix multiplication, thus impeding convergence. Third, obtaining the analytical gradient over the real device configurations,  $\partial \mathbf{W}^l(\Phi^l)/\Phi^l$ , can be very complex and prohibitive, as demonstrated in the case of an MZI-ONN [149].

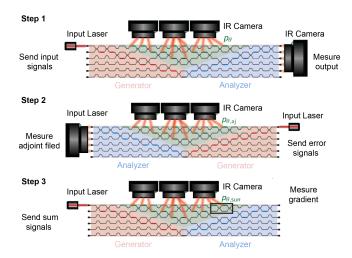

An adjoint-variable method was proposed theoretically to implement on-chip backpropagation by interfering with adjoint and forward fields [150]. Recent work has implemented the concept of in-situ backpropagation within a triangular MZI mesh [151]. As depicted in Fig. 10, the method involves forward and backward signal propagation, followed by gradient calculation. In step 1 and step 2, the "forward inference" signal x and "backward adjoint" signal  $x_{aj}$  are sent forward, respectively. Then the "sum" vector  $x - i(x_{aj})^*$  is send forward again. The gradient with respect to the phase variables can be finally obtained. However, this implementation requires additional power/phase monitors, faster microcontrollers, and more precise detectors, which increases hardware control complexity and imposes scalability concerns. Additionally, Ohno et al. attempted to design an MRR crossbar array capable of implementing matrix multiplication between the gradient and the transpose of the weight matrix [123], which is a fundamental operation in conventional backpropagation algorithms. While promising, this method has yet to be demonstrated on-chip. Besides, there is a line of works on on-chip learning protocols evaluated in simulation, which will be discussed in Section V-D.

# IV. PHOTONIC-ELECTRONIC AI ACCELERATOR: A GLANCE AT THE ARCHITECTURE LEVEL

Photonic AI computing is experiencing rapid advancements in both device and circuit-level innovations. To fully harness the potential of optical computing, it's imperative to develop comprehensive systems that combine PIC-based computing with key auxiliary components, such as memory and datapath elements. This necessitates architecture-level efforts to translate circuit-level innovations into practical frameworks suitable for real-world applications. However, the architecture-level study of photonic AI accelerators is still in its infancy, and limited research has been conducted in this direction. Given the significance of comprehending photonic AI accelerators, this section provides an overview from an architectural perspective, focusing deeply on the system components and covering various design considerations.

## A. Fully-Optical Vs. Photonic-Electronic Accelerators

1) Fully-Optical Accelerator: A fully optical accelerator refers to implementing all operations, including both computation and necessary nonlinear activation functions, entirely within the optical domain. Recent works have demonstrated the integration of optical computation and on-chip nonlinearity [32], [152], [153], [154]. Fully optical accelerators, although promising high bandwidth without the power consumption of E-O interference, still confront significant challenges due to scalability and practical implementation concerns. Firstly, the on-chip nonlinearity is not yet a mature scheme with low energy efficiency or flexibility compared to electronics, as discussed in Section III-C2. Secondly, the significant loss imposes a substantial requirement for optical power to meet the detection threshold. Additionally, computation errors will accumulate along the optical computing layers, deviating the final outcome significantly from the expected value.

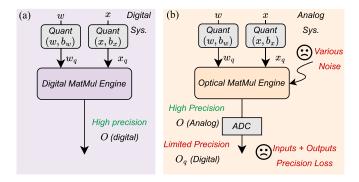

2) A More Practical Paradigm: Photonic-Electronic Accelerator: Given the challenges associated with practically implementing all-optical accelerators, the photonic-electronic hybrid accelerator emerges as a more feasible and competitive photonic AI solution [155], which is also the key focus in this section. The current hybrid accelerator setup takes advantage of both emerging photonics and mature electronics and builds a system with a tight integration of photonic and electronic integrated circuits. The intensive tensor operations are executed on optical parts in the analog domain, while the electronic segment includes digital memory for data storage and distribution, as well as essential units for data writing/reading, flow control, and minor data processing. Combining digital and analog domains results in a mixed-signal setup, therefore, requiring E-O/O-E, D/A, and A/D conversions. Although the conversion processes incur additional power consumption and delay, they also offer some advantages. For example, the A/D conversion process can be viewed as a denoising step, as it involves discretizing the continuous analog signals into digital representations. This discretization helps filter out noise that is present in the analog signals, avoiding error propagation.

## B. Architecture and Workload Mapping

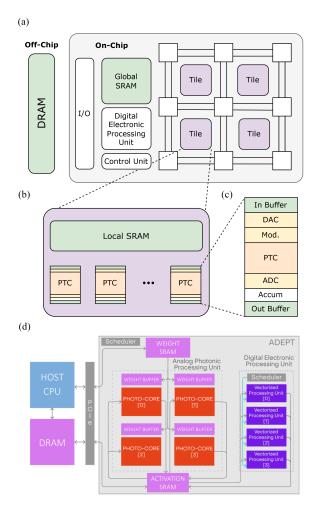

1) Architecture: The photonic-electronic accelerator can be classified into two types based on its application, which range from task-specific accelerators, such as those for CNNs [156], [157], [158], to general-purpose architectures [126], [159]. Despite their varied applications, these accelerators exhibit a similar generic high-level micro-architecture, as shown in Fig. 11.

Fig. 11. The generic photonic accelerator architecture. (a) A high-level representation of the full system architecture, including off-chip and on-chip components. (b) The architecture representation of a single tile. (c) The details of the linear computing unit using photonic components. (d) The system architecture of ADEPT interacting with peripheral components [159].